Chip Services

Chip Services

Products

Products

- Automotive and Industrial control

- Information Security

- Edge Computing& Network Communication

Products

Resources

Resources

Language

Language

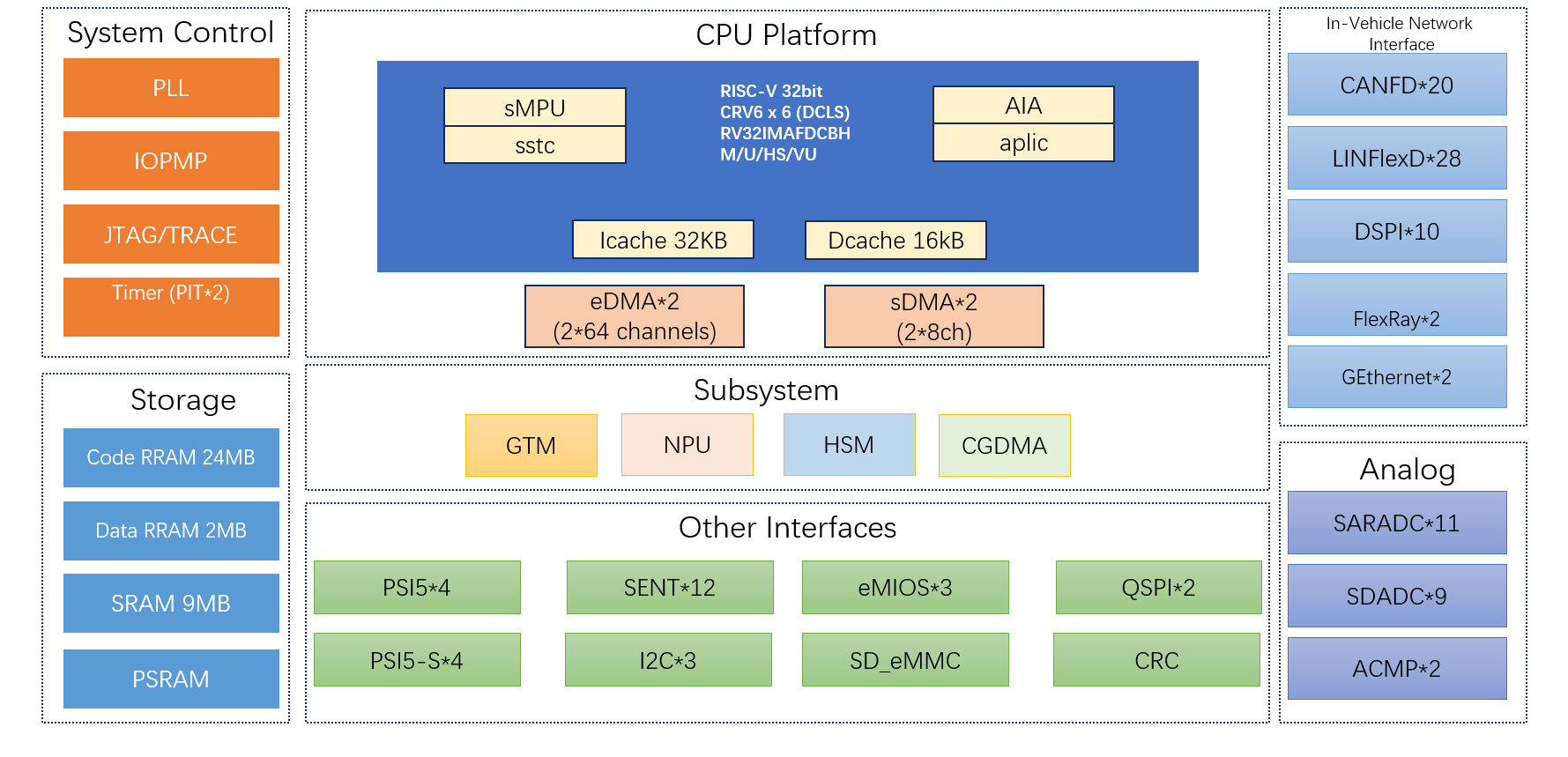

CCFC3009PT

Block Diagram

Features

● CPU Core

- Main Frequency: 500MHz (maximum)

- Superscalar RISC-V architecture with 12 cores (6+6): support lock-step and CPU cores can be decoupled/coupled as configration

- Double-precision FPU and DSP acceleration

- DMIPS: >10000

- Support hardware virtualization

● Rich on-chip resources and peripherals

- Embedded 24MB Code RRAM / 2MB Data RRAM, support hardware AB SWAP and OTA upgrade

- 9MB SRAM

- Integrating 2x GETH (SGMII and RGMII), 20x CANFD, 28x LIN, 2x FlexRay, 10x DSPI, 1x GTM4.1, 10x SARADC (total 110 channels), 9x SDADC

- Expandable external memory interfaces (EBI/EMMC/PSRAM)

- Integrated data routing CGDMA

● High security and reliability

- Full-stack security: MCU, MCAL, and libraries have achieved functional safety of ASIL-D

- Comply with EVITA-Full and Supports international and GM/T cryptographic algorithms

- Integrating post-quantum cryptographic algorithms

● Embedded AI processor

- NPU 0.3TOPS

Cross-domain integration, ADAS control, network switching/routing